IP核是FPGA芯片公司提供的逻辑功能块,在FPGA芯片中可以进行优化和预先配置,可以直接在用户设计的程序中使用,应用范围很广。在FPGA设计开发过程中使用IP核,可以大大的缩短开发周期,高度优化的IP核可以使FPG开发工程师专注于系统级开发,从而有助于加速开发进程,降低开发成本。

Xilinx公司提供的IP种类比较多,涉及到通信、图像、数学计算方面。这里我们主要介绍经常用到的IP核,PLL、FIFO、RAM。

FIFO定义

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,它与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据,其数据地址由内部读写指针自动加1完成,不能像普通存储器那样可以由地址线决定读取或写入某个指定的地址。

FIFO的分类

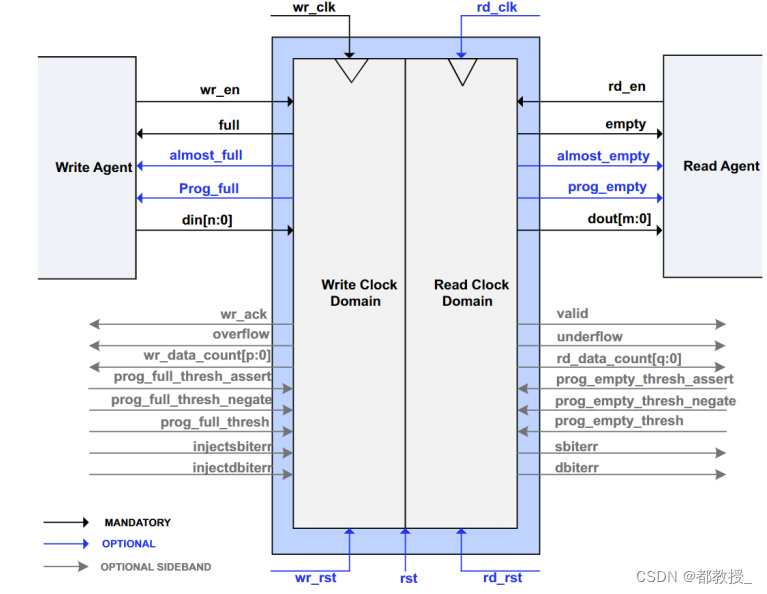

根据FIFO工作的时钟域,可以将FIFO分为同步FIFO和异步FIFO。同步FIFO是指读时钟和写时钟为同一个时钟。在时钟沿来临时同时发生读写操作。异步FIFO是指读写时钟不一致,读写时钟是互相独立的。

FIFO的工程创建

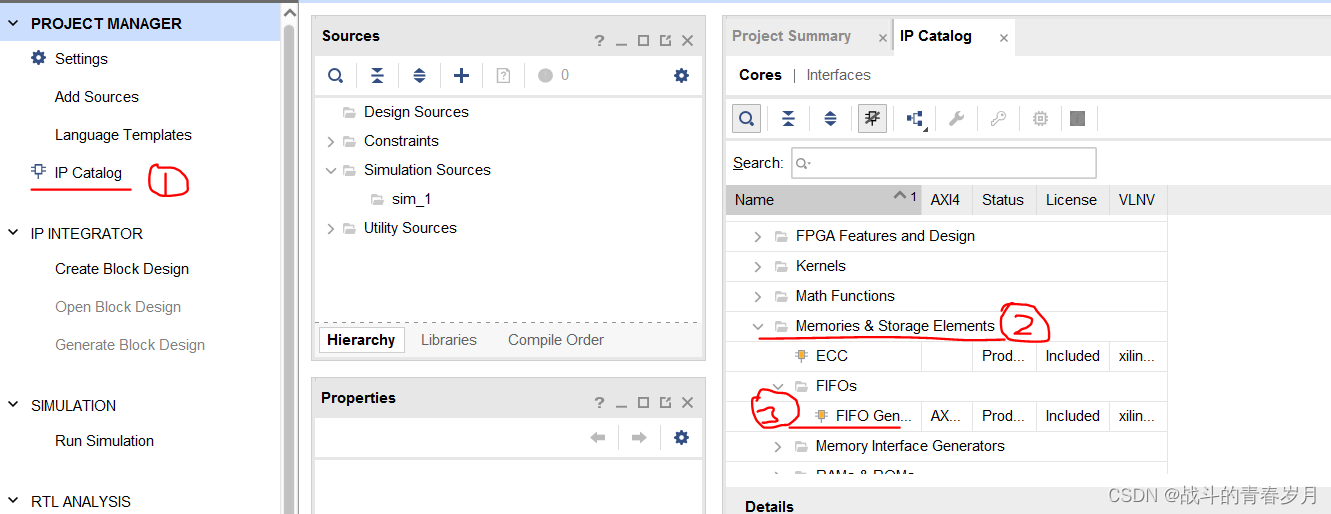

第一步:通过IP_Catalog打开IP核的目录

第二步:在Memories文件下查找FIFOS文件件

第三步:双击FIFO_Gen

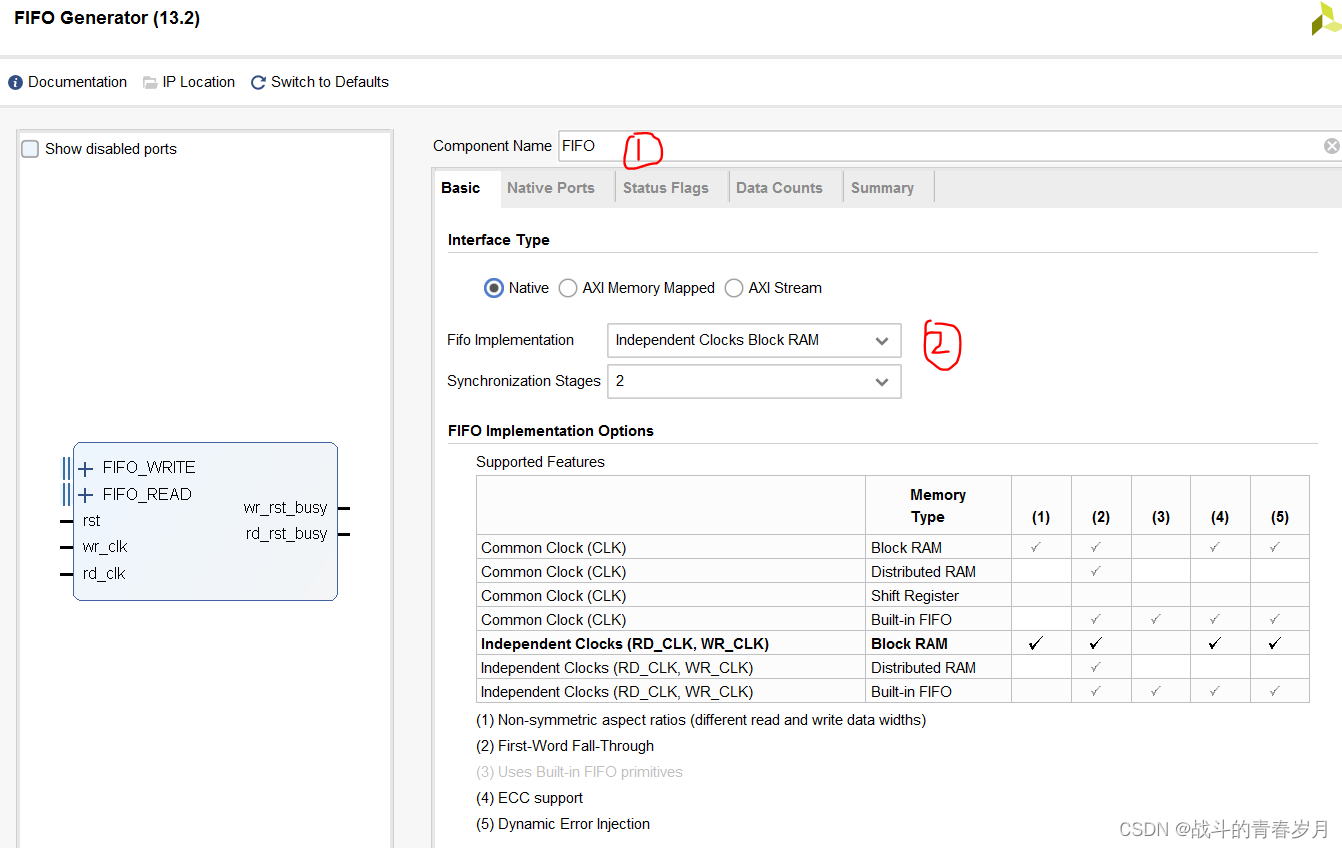

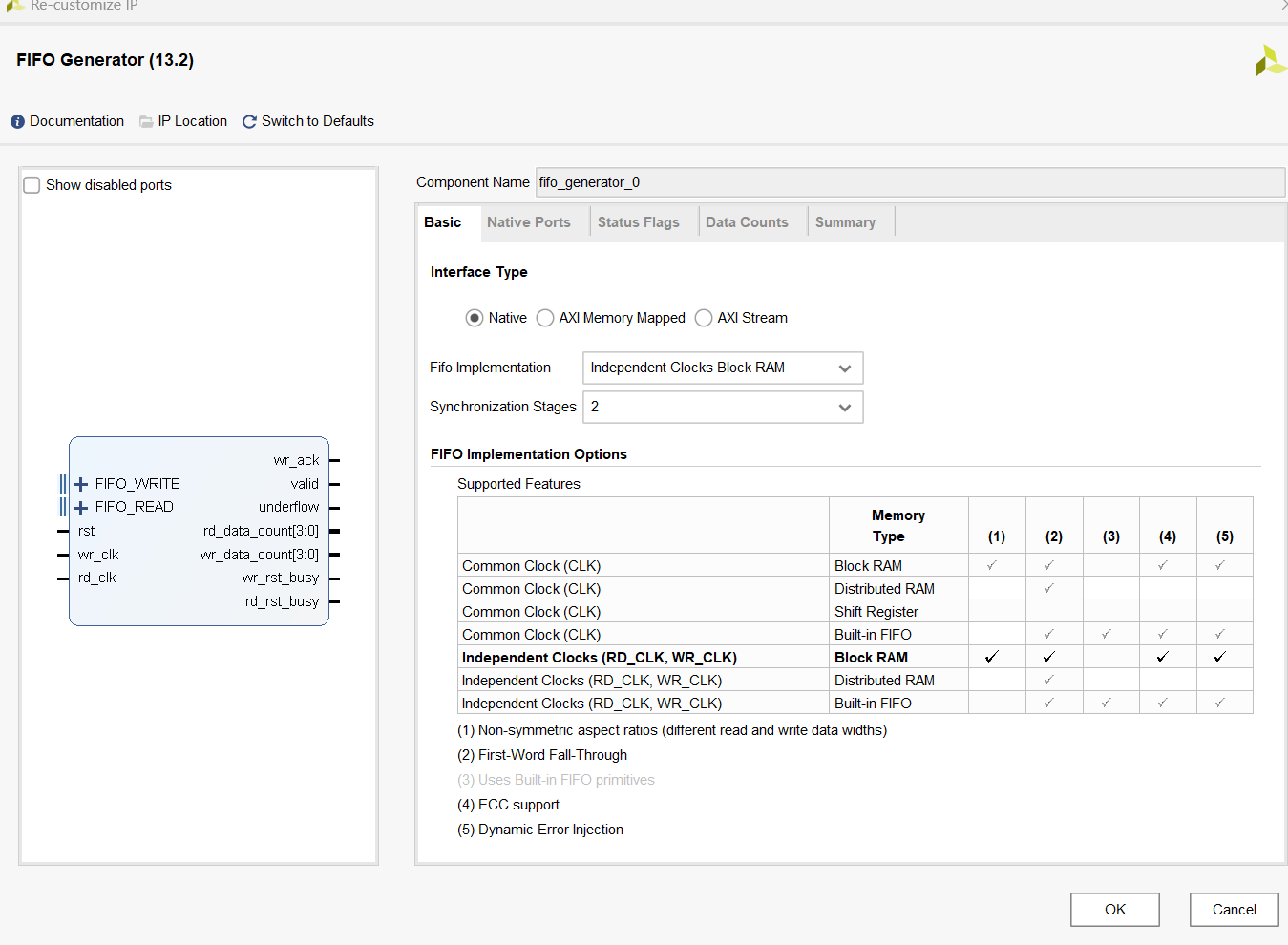

第一步:可以修改IP的名字

第二步:选择FIFO的存储资源类型

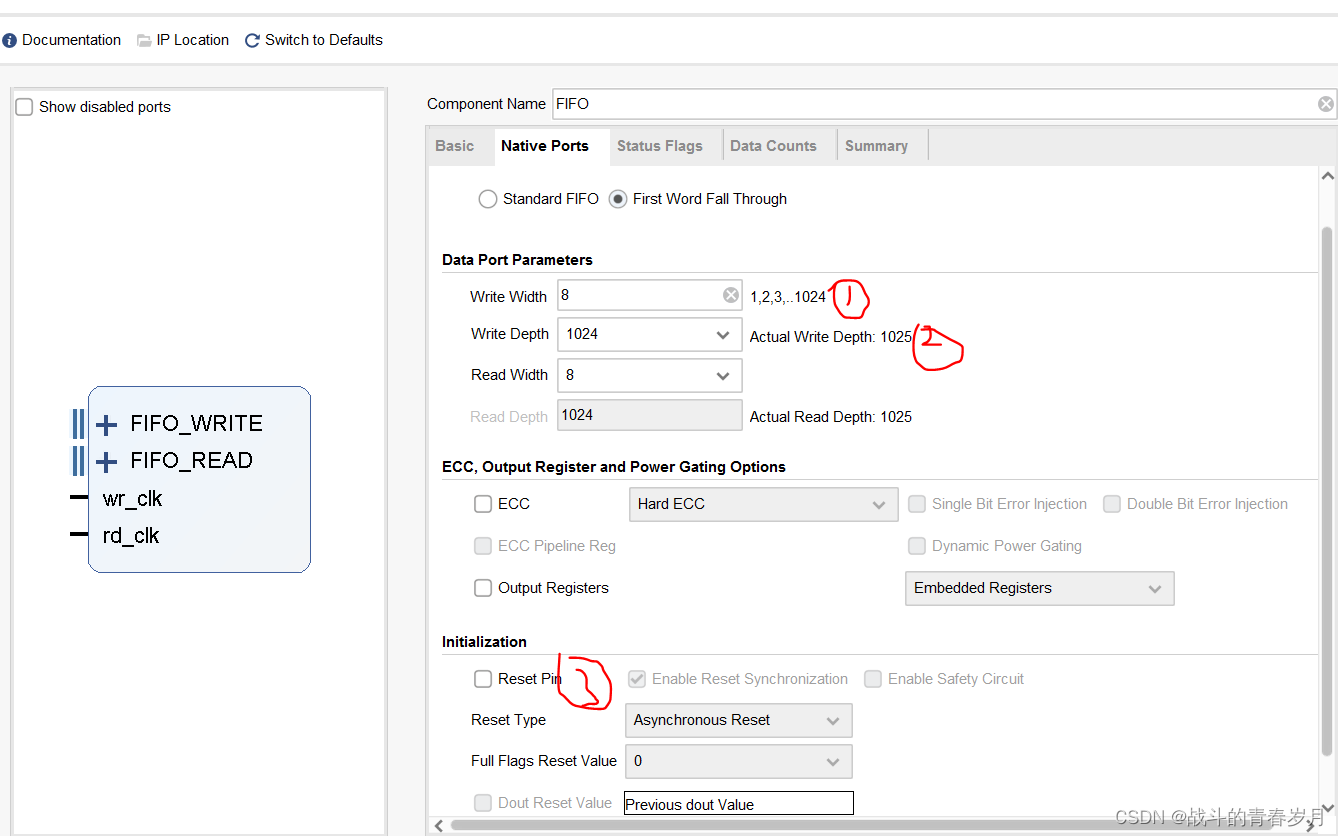

第一步:设置数据位宽

第二步:设置存储深度

第三步:复位信号可以根据情况选择需要或者不需要

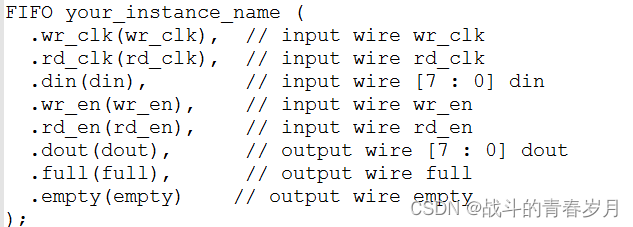

生成的FIFO_IP的接口如上图所示:

Wr_clk代表的写入工作时钟;Rd_clk代表的读取工作时钟;

Din代表的写入的数据端口;Wr_en代表的写使能信号;

Rd_en代表的读使能信号;Dout代表的从FIFO中读取的数据;

Full代表的FIFO存储空间满信号,当FIFO的存储空间全部存满数据后,该信号就会变成高电平;不满时该信号为低电平;

empty代表FIFO存储空间空信号;当FIFO中没有存储数据时,该信号就会变成高电平;有数据时就为低电平。

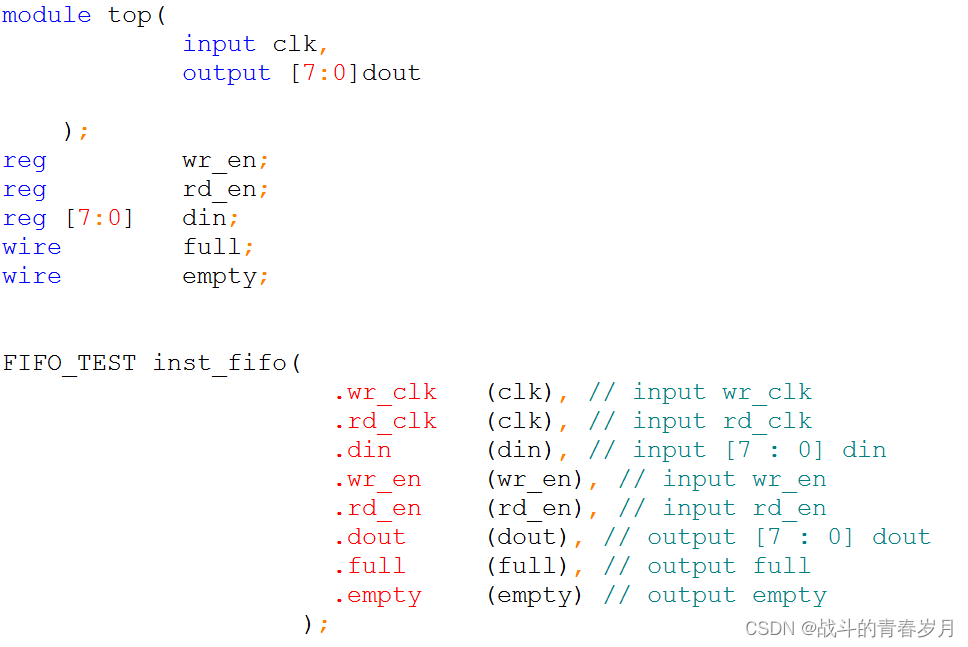

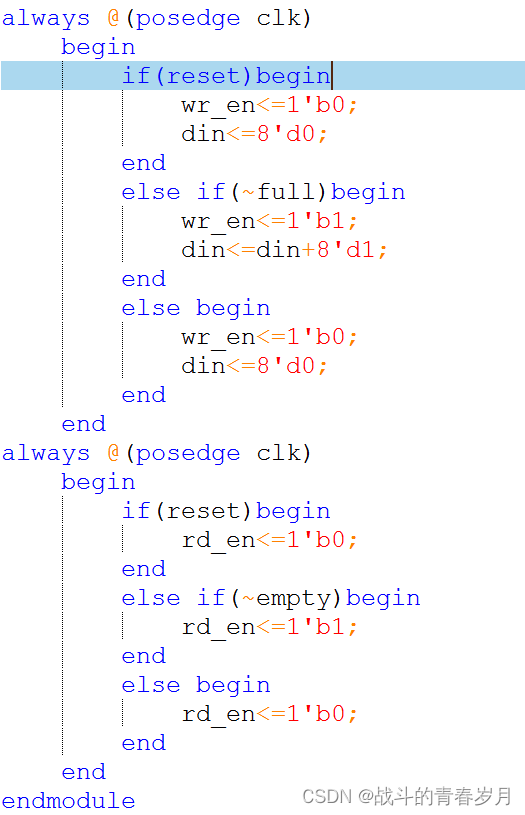

最后,将上图程序例化到top文件中。

如上图程序所示,分为三部分,

一部分是将FIFO的IP例化到top中;

第二部分是控制FIFO的写操作:通过判断FIFO的full信号,如果full信号为0时,就给FIFO写入数据;如果full信号为1时,就停止给FIFO写数据。

最后一部分是控制FIFO的读操作:通过判断FIFO的empty信号。如果empty为0时,就读取FIFO的数据,如果empty为1(F代表FIFO中没有数据),就停止读取。

![[<span style='color:red;'>FPGA</span> <span style='color:red;'>学习</span>记录] 快速开发的法宝——<span style='color:red;'>IP</span><span style='color:red;'>核</span>](https://img-blog.csdnimg.cn/img_convert/8d5753c8cf2335edbf455f1bb791f43d.png#pic_center)