快速了解数字逻辑门

文章目录

数字逻辑门是一种电子电路,它根据其输入上存在的数字信号的组合做出逻辑决策。

1、概述

数字逻辑门可以有多个输入,例如输入 A、B、C、D 等,但通常只有一个数字输出 (Q)。 各个逻辑门可以连接或级联在一起以形成具有任何所需数量的输入的逻辑门功能,或者形成组合和顺序类型电路,或者产生与标准门不同的逻辑门功能。

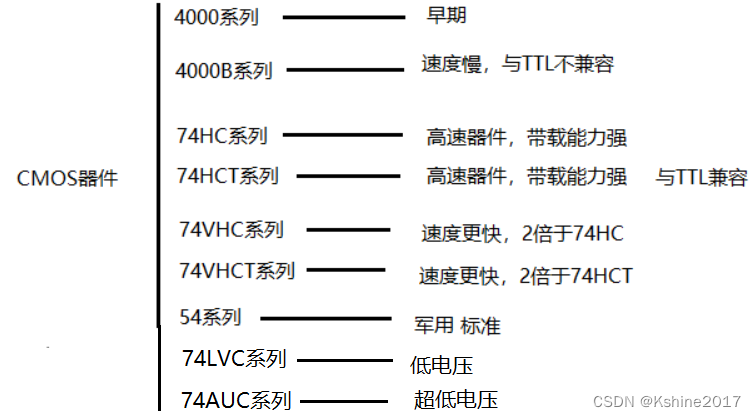

标准的商用数字逻辑门有两种基本系列或形式:TTL(代表晶体管-晶体管逻辑,例如 7400 系列)和 CMOS(代表互补金属氧化物硅,即 4000 系列芯片)。 TTL 或 CMOS 的这种表示法是指用于制造集成电路 (IC) 或更常见的“芯片”的逻辑技术。

一般来说,TTL逻辑IC的输入和输出电路使用NPN和PNP型双极结型晶体管,而CMOS逻辑IC则使用互补MOSFET或JFET型场效应晶体管。

除了 TTL 和 CMOS 技术之外,还可以通过将二极管、晶体管和电阻器连接在一起来制作简单的数字逻辑门,以产生 RTL、电阻晶体管逻辑门、DTL、二极管晶体管逻辑门或 ECL、发射极耦合逻辑门,但 与流行的 CMOS 系列相比,这些现在不太常见。

2、集成电路的分类

集成电路或更常见的名称是 IC,可以根据设计中可能包含的单个晶体管或“门”的数量将其分组为逻辑系列。 例如,一个简单的与门可能只包含几个单独的晶体管来运行。 而更复杂的微处理器芯片可以在一个晶圆上包含数十亿个单独的晶体管门。 集成电路根据逻辑门的数量或单个芯片内电路的复杂性进行分类,单个门的数量的一般分类如下:

- 小规模集成或 (SSI) – 在单个封装内包含最多 10 个晶体管或几个门,例如 AND、OR、NOT 门。

- 中等规模集成或 (MSI) – 单个封装内包含 10 到 100 个晶体管或数十个门,并执行加法器、解码器、计数器、触发器和多路复用器等数字操作。

- 大规模集成或 (LSI) – 100 到 1,000 个晶体管或数百个门,执行特定的数字操作,例如 I/O 芯片、存储器、算术和逻辑单元。

- 超大规模集成或 (VLSI) – 1,000 到 10,000 个晶体管或数千个门,并执行计算操作,例如处理器、大型存储器阵列和可编程逻辑器件。

- 超大规模集成或 (SLSI) – 单个封装内包含 10,000 至 100,000 个晶体管,并执行微处理器芯片、微控制器、基本 PIC 和计算器等计算操作。

- 超大规模集成或 (ULSI) – 超过 100 万个晶体管 – 用于计算机 CPU、GPU、视频处理器、微控制器、FPGA 和复杂 PIC 的大男孩。

虽然“超大规模”ULSI 分类不太常用,但代表集成电路复杂性的另一个集成级别被称为片上系统或简称 (SOC)。 这里的各个组件,如微处理器、存储器、外围设备、I/O 逻辑等,都在一块硅片上生产,代表着一个芯片内的整个电子系统,字面上将“集成”一词放入集成电路中 。

这些完整的集成芯片在一个封装内包含多达 1 亿个单独的硅 CMOS 晶体管门,通常用于移动电话、数码相机、微控制器、PIC 和机器人类型的应用。

3、摩尔定律

1965年,英特尔公司联合创始人戈登·摩尔对于半导体门技术的发展预测,“单个芯片上的晶体管和电阻器的数量将每18个月增加一倍”。 早在 1965 年,当戈登·摩尔 (Gordon Moore) 发表他的著名评论时,单个硅芯片或芯片上大约只有 60 个单独的晶体管门。

1971 年世界上第一个微处理器是 Intel 4004,它具有 4 位数据总线,单个芯片上包含约 2,300 个晶体管,工作频率约为 600kHz。 如今,英特尔公司已在其运行频率接近 4GHz 的新型四核 i7-2700K Sandy Bridge 64 位微处理器芯片上放置了惊人的 12 亿个独立晶体管门,并且随着更新更快的微处理器的出现,片上晶体管数量仍在不断增加。 并开发了微控制器。

4、数字逻辑状态

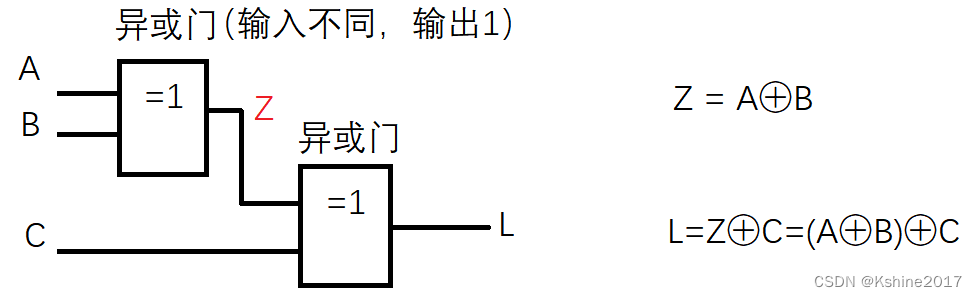

数字逻辑门是构建所有数字电子电路和基于微处理器的系统的基本构建块。 基本数字逻辑门对二进制数执行 AND、OR 和 NOT 逻辑运算。

在数字逻辑设计中,仅允许两个电压电平或状态,这些状态通常称为逻辑“1”和逻辑“0”,或高和低,或真和假。 这两种状态在布尔代数和标准真值表中分别用二进制数字“1”和“0”表示。

数字状态的一个很好的例子是简单的灯开关。 开关可以是“ON”或“OFF”,一种状态或另一种状态,但不能同时处于这两种状态。 那么我们可以将这些不同的数字状态之间的关系总结为:

| 布尔代数 | 布尔逻辑 | 电压状态 |

|---|---|---|

| 逻辑“1” | TRUE (T) | 高(H) |

| 逻辑“0” | FALSE (F) | 低(L) |

大多数数字逻辑门和数字逻辑系统使用“正逻辑”,其中逻辑电平“0”或“低”由零电压、0v或地表示,逻辑电平“1”或“高”由 更高的电压,例如+5伏,从一个电压电平切换到另一个电压电平,从逻辑电平“0”到“1”或从“1”到“0”尽可能快地进行 防止逻辑电路的任何错误操作。

还存在一种互补的“负逻辑”系统,其中逻辑“0”和逻辑“1”的值和规则相反,但在本关于数字逻辑门的教程部分中,我们仅将正逻辑约定称为 这是最常用的。

在标准 TTL(晶体管-晶体管逻辑)IC 中,输入和输出电压电平有一个预定义的电压范围,该范围准确定义了逻辑“1”电平和逻辑“0”电平,如下所示 。

![[蓝桥杯 2019 省赛 AB] 完全二叉树的权值](https://img-blog.csdnimg.cn/direct/fe4bf93cc14f4819bb505a482539629c.webp)